# 16-Bit Byte Wide, Low Glitch Multiplying DAC with 4-Quadrant Resistors

#### **FEATURES**

- True 16-Bit Performance over Industrial Temperature Range

- DNL and INL: 1LSB Max

- On-Chip 4-Quadrant Resistors Allow Precise

OV to 10V, OV to -10V or ±10V Outputs

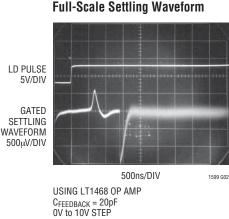

- 2µs Settling Time to 0.0015% (with LT®1468)

- Asynchronous Clear Pin Resets to Zero Scale or Midscale

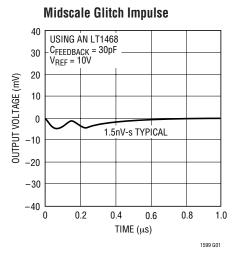

- Glitch Impulse: 1.5nV-s

- 24-Lead SSOP Package

- Low Power Consumption: 10µW Typ

- Power-On Reset to Zero Scale or Midscale

- 2-Byte Parallel Digital Interface

- Available in 24-Lead SSOP and PDIP Packages

#### **APPLICATIONS**

- Process Control and Industrial Automation

- Direct Digital Waveform Generation

- Software-Controlled Gain Adjustment

- Automatic Test Equipment

#### DESCRIPTION

The LTC®1599 is a 2-byte parallel input 16-bit multiplying current output DAC that operates from a single 5V supply. INL and DNL are accurate to 1LSB over the industrial temperature range in both 2- and 4-quadrant multiplying modes. True 16-bit 4-quadrant multiplication is achieved with on-chip 4-quadrant multiplication resistors.

The LTC1599 is available in 24-pin PDIP and SSOP packages and is specified over the commercial and industrial temperature ranges. The device includes an internal deglitcher circuit that reduces the glitch impulse to 1.5nV-s (typ). The asynchronous CLR pin resets the LTC1599 to zero scale when the CLVL pin is at a logic low and to midscale when the CLVL pin is at a logic high.

For a full 16-bit wide parallel interface current output DAC, refer to the LTC1597 data sheet. For serial interface 16-bit current output DACs, refer to the LTC1595/LTC1596 data sheet

7, LTC and LT are registered trademarks of Linear Technology Corporation.

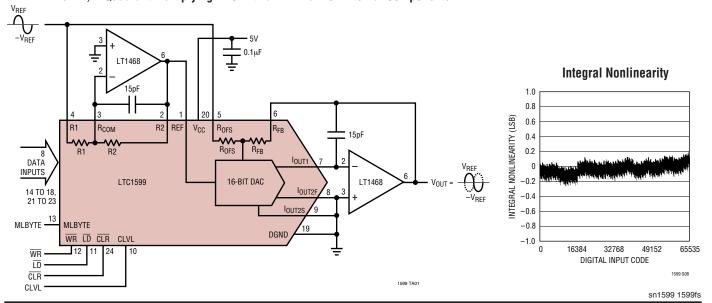

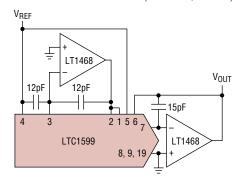

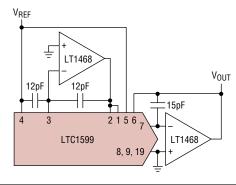

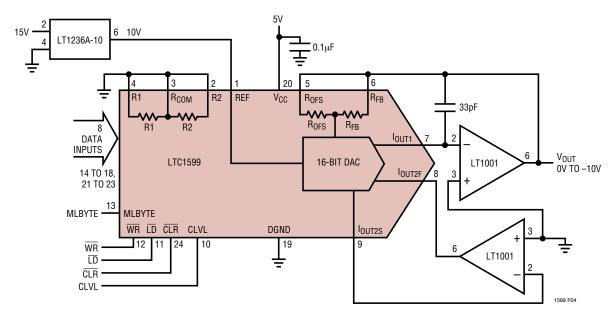

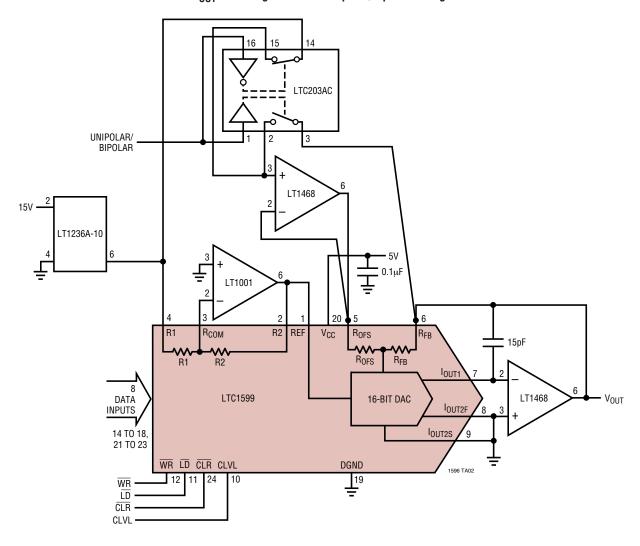

# TYPICAL APPLICATION

A 16-Bit, 4-Quadrant Multiplying DAC with a Minimum of External Components

### **ABSOLUTE MAXIMUM RATINGS**

| ( | (Note 1)                                                            |                               |

|---|---------------------------------------------------------------------|-------------------------------|

| ١ | V <sub>CC</sub> to DGND                                             | 0.3V to 7V                    |

|   | $REF,R_{OFS},R_{FB},R1,R2$ to $DGND$ .                              | ±25V                          |

|   | R <sub>COM</sub>                                                    | 0.3V to 12V                   |

|   | Digital Inputs to DGND                                              | $-0.3V$ to $(V_{CC} + 0.3V)$  |

|   | I <sub>OUT1</sub> , I <sub>OUT2F</sub> , I <sub>OUT2S</sub> to DGND | $-0.3V$ to( $V_{CC} + 0.3V$ ) |

|   | Maximum Junction Temperature .                                      | 125°C                         |

| ( | Operating Temperature Range                                         |                               |

|   | LTC1599C                                                            | 0°C to 70°C                   |

|   | LTC15991                                                            | 40°C to 85°C                  |

|   | Storage Temperature Range                                           | 65°C to 150°C                 |

|   | Lead Temperature (Soldering, 10                                     | sec) 300°C                    |

|   |                                                                     |                               |

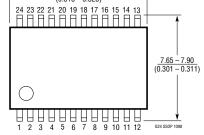

# PACKAGE/ORDER INFORMATION

| TOP VIEW                                                                                                                                                                                                                                                                            | 24 CLR | ORDER PART<br>NUMBER                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|

| R2 2 R <sub>COM</sub> 3 R1 4 R <sub>OFS</sub> 5 R <sub>FB</sub> 6 l <sub>OUT1</sub> 7 l <sub>OUT2F</sub> 8 l <sub>OUT2S</sub> 9 CLVL 10 LD 11 WR 12 G PACKAGE 24-LEAD PLASTIC SSOP  T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 95 T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 55 |        | LTC1599ACG<br>LTC1599BCG<br>LTC1599AIG<br>LTC1599BIG<br>LTC1599ACN<br>LTC1599BCN<br>LTC1599AIN<br>LTC1599BIN |

Consult factory for Military grade parts.

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V \pm 10\%$ ,  $V_{REF} = 10V$ ,  $I_{OUT1} = I_{OUT2F} = I_{OUT2S} = DGND = 0V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$  unless otherwise noted.

| SYMBOL           | PARAMETER                    | CONDITIONS                                                                              |   | MIN | LTC1599B<br>TYP | MAX        | MIN | LTC1599A<br>TYP | MAX        | UNITS      |

|------------------|------------------------------|-----------------------------------------------------------------------------------------|---|-----|-----------------|------------|-----|-----------------|------------|------------|

| Accuracy         |                              |                                                                                         |   |     |                 |            |     |                 |            | -          |

|                  | Resolution                   |                                                                                         | • | 16  |                 |            | 16  |                 |            | Bits       |

|                  | Monotonicity                 |                                                                                         | • | 16  |                 |            | 16  |                 |            | Bits       |

| INL              | Integral Nonlinearity        | T <sub>A</sub> = 25°C (Note 2)<br>T <sub>MIN</sub> to T <sub>MAX</sub>                  | • |     |                 | ±2<br>±2   |     | ±0.25<br>±0.35  | ±1<br>±1   | LSB<br>LSB |

| DNL              | Differential Nonlinearity    | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>                           | • |     |                 | ±1<br>±1   |     | ±0.2<br>±0.2    | ±1<br>±1   | LSB<br>LSB |

| GE               | Gain Error                   | Unipolar Mode<br>T <sub>A</sub> = 25°C (Note 3)<br>T <sub>MIN</sub> to T <sub>MAX</sub> | • |     |                 | ±16<br>±24 |     | 2<br>3          | ±16<br>±16 | LSB<br>LSB |

|                  |                              | Bipolar Mode<br>T <sub>A</sub> = 25°C (Note 3)<br>T <sub>MIN</sub> to T <sub>MAX</sub>  | • |     |                 | ±16<br>±24 |     | 2<br>3          | ±16<br>±16 | LSB<br>LSB |

|                  | Gain Temperature Coefficient | ∆Gain/∆Temperature (Note 4)                                                             | • |     | 1               | 3          |     | 1               | 3          | ppm/°C     |

|                  | Bipolar Zero Error           | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>                           | • |     |                 | ±10<br>±16 |     |                 | ±5<br>±8   | LSB<br>LSB |

| I <sub>LKG</sub> | OUT1 Leakage Current         | T <sub>A</sub> = 25°C (Note 5)<br>T <sub>MIN</sub> to T <sub>MAX</sub>                  | • |     |                 | ±5<br>±15  |     |                 | ±5<br>±15  | nA<br>nA   |

| PSRR             | Power Supply Rejection       | V <sub>CC</sub> = 5V ±10%                                                               | • |     | ±1              | ±2         |     | ±1              | ±2         | LSB/V      |

LINEAR

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V \pm 10\%$ ,  $V_{REF} = 10V$ ,  $I_{OUT1} = I_{OUT2F} = I_{OUT2S} = DGND = 0V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$  unless otherwise noted.

| SYMBOL                             | PARAMETER                        | CONDITIONS                                                                                        |   | MIN | TYP       | MAX       | UNITS      |

|------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------|---|-----|-----------|-----------|------------|

| Reference                          | Input                            |                                                                                                   |   |     |           |           |            |

| R <sub>REF</sub>                   | DAC Input Resistance (Unipolar)  | (Note 6)                                                                                          | • | 4.5 | 6         | 10        | kΩ         |

| R1, R2                             | R1, R2 Resistance (Bipolar)      | (Notes 6, 13)                                                                                     | • | 9   | 14        | 20        | kΩ         |

| R <sub>OFS</sub> , R <sub>FB</sub> | Feedback and Offset Resistances  | (Note 6)                                                                                          | • | 9   | 13.5      | 20        | kΩ         |

| AC Perforn                         | nance (Note 4)                   |                                                                                                   |   |     |           |           |            |

|                                    | Output Current Settling Time     | (Notes 7, 8)                                                                                      |   |     | 1         |           | μS         |

|                                    | Midscale Glitch Impulse          | (Note 12)                                                                                         |   |     | 1.5       |           | nV-s       |

|                                    | Digital-to-Analog Glitch Impulse | (Note 9)                                                                                          |   |     | 1         |           | nV-s       |

|                                    | Multiplying Feedthrough Error    | $V_{REF} = \pm 10V$ , 10kHz Sine Wave                                                             |   |     | 1         |           | $mV_{P-P}$ |

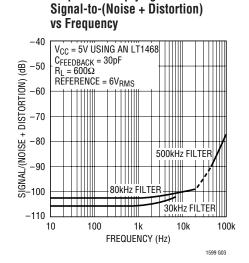

| THD                                | Total Harmonic Distortion        | (Note 10)                                                                                         |   |     | 108       |           | dB         |

|                                    | Output Noise Voltage Density     | (Note 11)                                                                                         |   |     | 10        |           | nV/√Hz     |

| Analog Ou                          | tputs (Note 4)                   |                                                                                                   |   |     |           |           |            |

| C <sub>OUT</sub>                   | Output Capacitance (Note 4)      | DAC Register Loaded to All 1s: C <sub>OUT1</sub> DAC Register Loaded to All 0s: C <sub>OUT1</sub> | • |     | 115<br>70 | 130<br>80 | pF<br>pF   |

| Digital Inp                        | uts                              |                                                                                                   |   |     |           |           |            |

| V <sub>IH</sub>                    | Digital Input High Voltage       |                                                                                                   | • | 2.4 |           |           | V          |

| V <sub>IL</sub>                    | Digital Input Low Voltage        |                                                                                                   | • |     |           | 0.8       | V          |

| I <sub>IN</sub>                    | Digital Input Current            |                                                                                                   | • |     | 0.001     | ±1        | μΑ         |

| C <sub>IN</sub>                    | Digital Input Capacitance        | (Note 4) V <sub>IN</sub> = 0V                                                                     | • |     |           | 8         | pF         |

| Timing Ch                          | aracteristics                    |                                                                                                   |   |     |           |           |            |

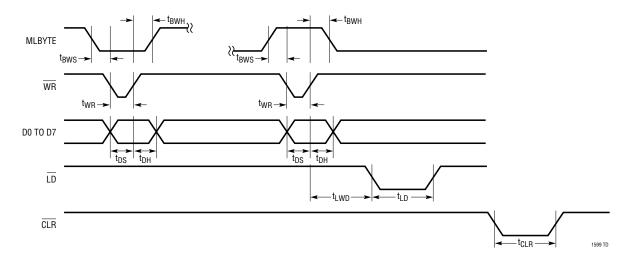

| t <sub>DS</sub>                    | Data to WR Setup Time            |                                                                                                   | • | 80  | 20        |           | ns         |

| t <sub>DH</sub>                    | Data to WR Hold Time             |                                                                                                   | • | 0   | -12       |           | ns         |

| t <sub>WR</sub>                    | WR Pulse Width                   |                                                                                                   | • | 80  | 25        |           | ns         |

| t <sub>BWS</sub>                   | MLBYTE to WR Setup Time          |                                                                                                   | • | 0   | -12       |           | ns         |

| t <sub>BWH</sub>                   | MLBYTE to WR Hold Time           |                                                                                                   | • | 0   | -12       |           | ns         |

| $t_{LD}$                           | LD Pulse Width                   |                                                                                                   | • | 150 | 55        |           | ns         |

| t <sub>CLR</sub>                   | Clear Pulse Width                |                                                                                                   | • | 150 | 50        |           | ns         |

| $t_{LWD}$                          | WR to LD Delay Time              |                                                                                                   | • | 0   |           |           | ns         |

| Power Sup                          | ply                              |                                                                                                   |   |     |           |           |            |

| V <sub>CC</sub>                    | Supply Voltage                   |                                                                                                   | • | 4.5 | 5         | 5.5       | V          |

| I <sub>CC</sub>                    | Supply Current                   | Digital Inputs = 0V or V <sub>CC</sub>                                                            | • |     |           | 10        | μΑ         |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2:  $\pm 1LSB = \pm 0.0015\%$  of full scale =  $\pm 15.3$ ppm of full scale.

Note 3: Using internal feedback resistor.

Note 4: Guaranteed by design, not subject to test.

**Note 5:** I<sub>(OUT1)</sub> with DAC register loaded to all 0s.

Note 6: Typical temperature coefficient is 100ppm/°C.

**Note 7:**  $I_{OUT1}$  load =  $100\Omega$  in parallel with 13pF.

**Note 8:**  $\underline{\text{To}}$  0.0015% for a full-scale change, measured from the falling edge of  $\overline{\text{LD}}$ .

**Note 9:**  $V_{REF} = \underline{OV}$ . DAC register contents changed from all 0s to all 1s or all 1s to all 0s.  $\overline{LD}$  high,  $\overline{WR}$  and MLBYTE pulsed.

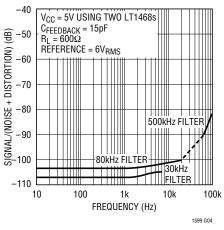

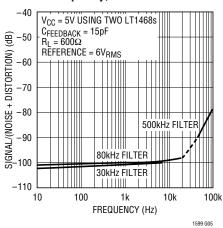

Note 10:  $V_{REF} = 6V_{RMS}$  at 1kHz. DAC register loaded with all 1s.

$R_L$  = 600 $\Omega$ . Unipolar mode op amp = LT1468.

**Note 11:** Calculation from  $e_n = \sqrt{4kTRB}$  where: k = Boltzmann constant  $(J/^{\circ}K)$ , R = resistance  $(\Omega)$ , T = temperature  $(^{\circ}K)$ , B = bandwidth (Hz).

Note 13: R1 and R2 are measured between R1 and  $R_{COM}$ , R2 and  $R_{COM}$ .

#### TYPICAL PERFORMANCE CHARACTERISTICS

**Unipolar Multiplying Mode**

Bipolar Multiplying Mode Signal-to-(Noise + Distortion) vs Frequency, Code = All Zeros

Bipolar Multiplying Mode Signal-to-(Noise + Distortion) vs Frequency, Code = All Ones

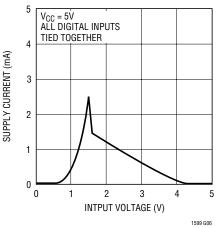

**Supply Current vs Input Voltage**

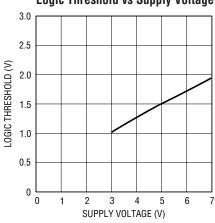

Logic Threshold vs Supply Voltage

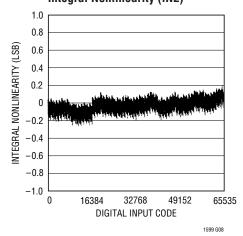

Integral Nonlinearity (INL)

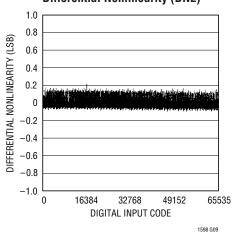

Differential Nonlinearity (DNL)

## TYPICAL PERFORMANCE CHARACTERISTICS

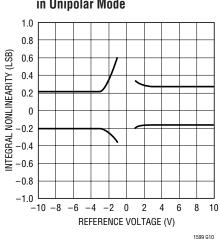

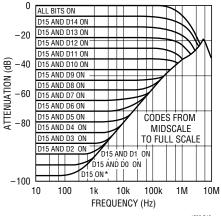

Integral Nonlinearity vs Reference Voltage in Unipolar Mode

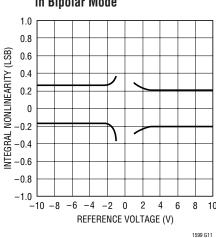

Integral Nonlinearity vs Reference Voltage in Bipolar Mode

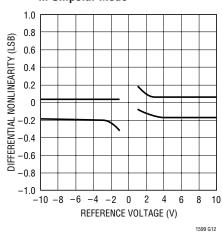

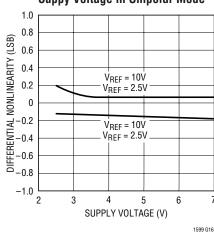

Differential Nonlinearity vs Reference Voltage in Unipolar Mode

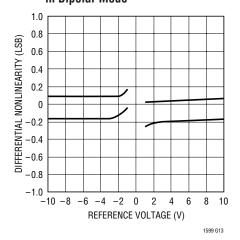

Differential Nonlinearity vs Reference Voltage in Bipolar Mode

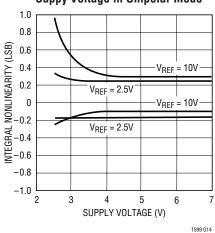

Integral Nonlinearity vs Suppy Voltage in Unipolar Mode

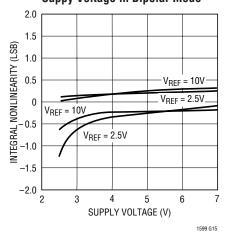

Integral Nonlinearity vs Suppy Voltage in Bipolar Mode

#### Differential Nonlinearity vs Suppy Voltage in Unipolar Mode

#### TYPICAL PERFORMANCE CHARACTERISTICS

#### Differential Nonlinearity vs Supply Voltage in Bipolar Mode

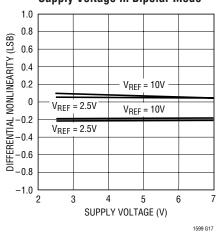

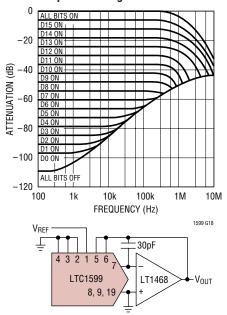

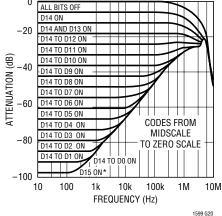

#### Unipolar Multiplying Mode Frequency Response vs Digital Code

#### Bipolar Multiplying Mode Frequency Response vs Digital Code

####

**Bipolar Multiplying Mode Frequency**

Response vs Digital Code

\*DAC ZERO VOLTAGE OUTPUT LIMITED BY BIPOLAR ZERO ERROR TO -96dB TYPICAL (-78dB MAX, A GRADE)

\*DAC ZERO VOLTAGE OUTPUT LIMITED BY BIPOLAR ZERO ERROR TO –96dB TYPICAL (–78dB MAX, A GRADE)

#### PIN FUNCTIONS

**REF (Pin 1):** Reference Input. Typically  $\pm 10V$ , accepts up to  $\pm 25V$ . In 2-quadrant mode, this pin is the reference input. In 4-quadrant mode, this pin is driven by external inverting reference amplifier.

**R2** (Pin 2): 4-Quadrant Resistor R2. Typically  $\pm 10V$ , accepts up to  $\pm 25V$ . In 2-quadrant operation, connect this pin to ground. In 4-quadrant mode tie to the REF pin and to the output of an external amplifier. See Figures 1 and 3.

**R<sub>COM</sub>** (**Pin 3**): Center Tap Point of the Two 4-Quadrant Resistors R1 and R2. Normally tied to the inverting input of an external amplifier in 4-quadrant operation, otherwise connect this pin to ground. See Figures 1 and 3. The absolute maximum voltage range on this pin is -0.3V to 12V.

**R1** (**Pin 4**): 4-Quadrant Resistor R1. Typically  $\pm 10V$ , accepts up to  $\pm 25V$ . In 2-quadrant operation connect this pin to ground. In 4-quadrant mode tie to R<sub>OFS</sub> (Pin 5). See Figures 1 and 3.

**R<sub>0FS</sub>** (**Pin 5**): Bipolar Offset Resistor. Typically swings  $\pm 10V$ , accepts up to  $\pm 25V$ . In 2-quadrant operation, tie to R<sub>FB</sub>. In 4-quadrant operation tie to R1.

$R_{FB}$  (Pin 6): Feedback Resistor. Normally tied to the output of the current to voltage converter op amp. Typically swings  $\pm 10V$ . Swings  $\pm V_{REF}$ .

$I_{OUT1}$  (Pin 7): DAC Current Output. Tie to the inverting input of the current to voltage converter op amp.

**I<sub>OUT2F</sub> (Pin 8):** Force Complement Current Output. Normally tied to ground.

**I**<sub>OUT2S</sub> (**Pin 9**): Sense Complement Current Output. Normally tied to ground.

**CLVL (Pin 10):** Clear Level. CLVL = 0, selects reset to zero code. CLVL = 1, selects reset to midscale code. Normally hardwired to a logic high or a logic low.

**LD** (**Pin 11**): DAC Digital Input Load Control Input. When LD is taken to a logic low, data is loaded from the input register into the DAC register, updating the DAC output.

**WR (Pin 12): DAC** Digital Write Control Input. When WR is taken to a logic low, data is loaded from the 8 digital input pins into the 16-bit wide input register. The MLBYTE pin determines whether the MSB or LSB byte is loaded.

**MLBYTE (Pin 13):** MSB or <u>LSB</u> Byte Select. When MLBYTE is taken to a logic low and  $\overline{WR}$  is taken to a logic low, data is loaded from the 8 digital input pins into the first 8 bits of the 16-bit wide input register. When MLBYTE is taken to a logic high and  $\overline{WR}$  is taken to a logic low, data is loaded from the 8 digital input pins into the 8 MSB bits of the input register.

D7 to D3 (Pins 14 to 18): Digital Input Data Bits.

**DGND (Pin 19):** Digital Ground. Tie to ground.

**V<sub>CC</sub> (Pin 20):** The Positive Supply Input.  $4.5 \text{V} \le \text{V}_{CC} \le 5.5 \text{V}$ . Requires a bypass capacitor to ground.

D2 to D0 (Pins 21 to 23): Digital Input Data Bits.

CLR (Pin 24): Digital Clear Control Function for the DAC. When CLR and CLVL are taken to a logic low, the DAC output and all internal registers are set to zero code. When CLR is taken to a logic low and CLVL is taken to a logic high, the DAC output and all internal registers are set to midscale code.

# TRUTH TABLE

Table 1

|     | CONTROL INPUTS |        |    |                                                                                                                                                                                                                                                                                               |

|-----|----------------|--------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR | WR             | MLBYTE | LD | REGISTER OPERATION                                                                                                                                                                                                                                                                            |

| 0   | Χ              | Χ      | Χ  | Reset Input and DAC Registers to Zero Scale When CLVL = 0 and Midscale When CLVL = 1                                                                                                                                                                                                          |

| 1   |                | 0      | 1  | Load the LSB Byte of the Input Register with All 8 Data Bits                                                                                                                                                                                                                                  |

| 1   |                | 1      | 1  | Load the MSB Byte of the Input Register with All 8 Data Bits                                                                                                                                                                                                                                  |

| 1   | 1              | Х      |    | Load the DAC Register with the Contents of the Input Register                                                                                                                                                                                                                                 |

| 1   | 1              | Χ      | 1  | No Register Operation                                                                                                                                                                                                                                                                         |

| 1   |                | Х      |    | Flow-Through Mode. The DAC Register and the Selected Input Register Are Transparent. The Unselected Input Register Retains Its Previous Data Byte. Note Only One Byte Is Transparent at a Time, the Selected Byte Being Determined By the Logic Value of MLBYTE Prior to WR Being Pulsed Low. |

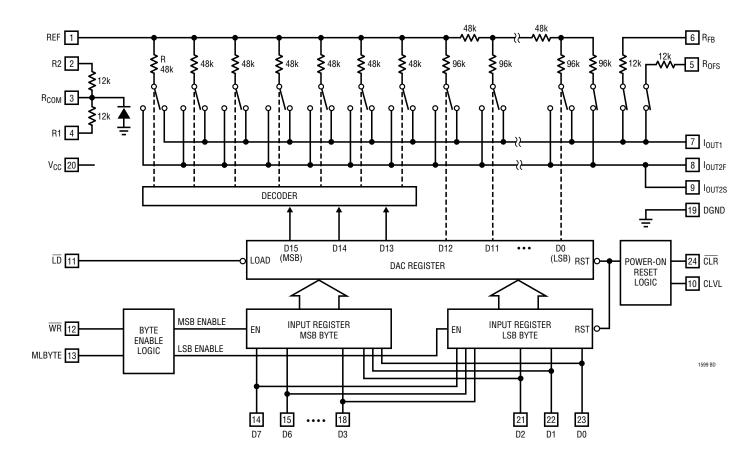

# **BLOCK DIAGRAM**

# TIMING DIAGRAM

#### **Description**

The LTC1599 is a 16-bit multiplying, current output DAC with a 2-byte (8-bit wide) digital interface. The device operates from a single 5V supply and provides both unipolar 0V to -10V or 0V to 10V and bipolar  $\pm 10V$  output ranges from a 10V or -10V reference input. It has three additional precision resistors on chip for bipolar operation. Refer to the Block Diagram regarding the following description.

The 16-bit DAC consists of a precision R-2R ladder for the 13LSBs. The 3MSBs are decoded into seven seaments of resistor value R (48k typ). Each of these segments and the R-2R ladder carries an equally weighted current of one eighth of full scale. The feedback resistor RFB and 4-quadrant resistor R<sub>OFS</sub> have a value of R/4. 4-quadrant resistors R1 and R2 have a magnitude of R/4. R1 and R2 together with an external op amp (see Figure 4) inverts the reference input voltage and applies it to the 16-bit DAC input REF, in 4-quadrant operation. The REF pin presents a constant input impedance of R/8 in unipolar mode and R/12 in bipolar mode. The output impedance of the current output pin Inut varies with DAC input code. The Inut capacitance due to the NMOS current steering switches also varies with input code from 70pF to 115pF. Inutzer and I<sub>OUT2S</sub> are normally tied to the system analog ground. An added feature of the LTC1599 is a proprietary deglitcher that reduces glitch impulse to 1.5nV-s over the DAC output voltage range.

#### **Digital Section**

The LTC1599 has a byte wide (8-bit), digital input data bus. The device is double-buffered with two 16-bit registers. The double-buffered feature permits the update of several DACs simultaneously. The input register is loaded directly from an 8-bit (or higher) microprocessor bus in a two step sequence. The MLBYTE pin selects whether the 8 input data bits are loaded into the LSB or the MSB byte of the input register. When MLBYTE is brought to a logic low level and  $\overline{WR}$  is given a logic low going pulse, the 8 data bits are loaded into the LSB byte of the input register. Conversely, when MLBYTE is brought to a logic high level and  $\overline{WR}$  is given a logic low going pulse, the 8 data bits are loaded into the MSB byte of the input register. If  $\overline{WR}$  is

brought to a logic low level, the existing level of MLBYTE determines which byte is loaded into the input register. If the logic level of MLBYTE is changed while WR remains low, no change will occur. This is because WR is an edge triggered signal and once it goes low it locks out any further changes in MLBYTE. WR must be brought high and then low again to accept the new MLBYTE condition. The second register (DAC register) is updated with the data from the input register when the  $\overline{LD}$  pin is brought to a logic low level. Updating the DAC register updates the DAC output with the new data. The deglitcher is activated on the falling edge of the  $\overline{LD}$  pin. The asynchronous clear pin resets the LTC1599 to zero scale when the CLVL pin is at a logic low level and to midscale when the CLVL pin is at a logic high level. CLR resets both the input and DAC registers. The device also has a power-on reset. Table 1 shows the truth table for the device.

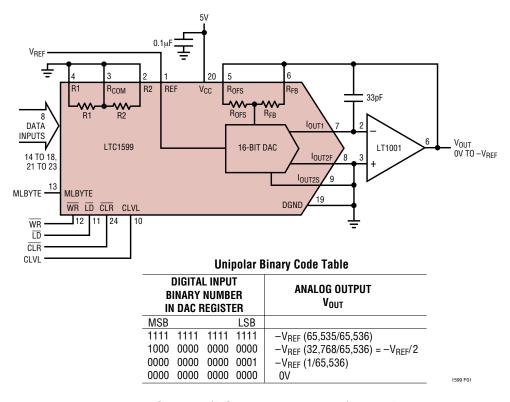

# Unipolar Mode (2-Quadrant Multiplying, $V_{OUT} = 0V \text{ to } - V_{REF}$ )

The LTC1599 can be used with a single op amp to provide 2-quadrant multiplying operation as shown in Figure 1. With a fixed -10V reference, the circuit shown gives a precision unipolar 0V to 10V output swing.

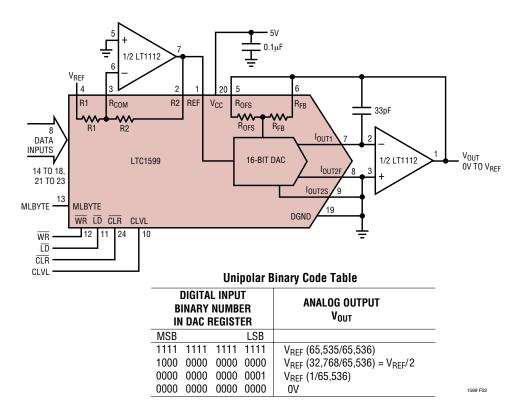

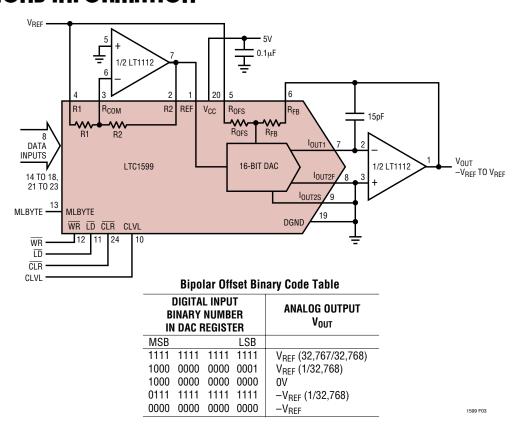

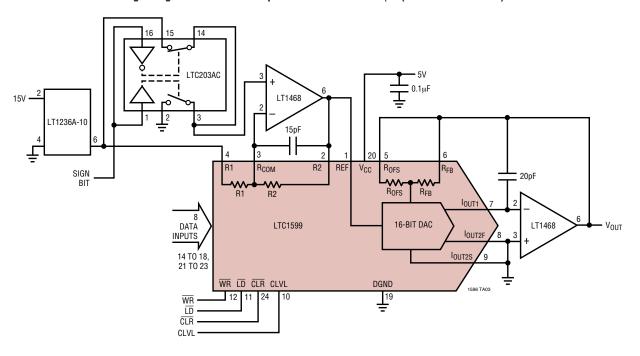

# Bipolar Mode (4-Quadrant Multiplying, $V_{OUT} = -V_{REF}$ to $V_{REF}$ )

The LTC1599 contains on chip all the 4-quadrant resistors necessary for bipolar operation. 4-quadrant multiplying operation can be achieved with a minimum of external components, a capacitor and a dual op amp, as shown in Figure 3. With a fixed 10V reference, the circuit shown gives a precision bipolar –10V to 10V output swing.

#### **Op Amp Selection**

Because of the extremely high accuracy of the 16-bit LTC1599, careful thought should be given to op amp selection in order to achieve the exceptional performance of which the part is capable. Fortunately, the sensitivity of INL and DNL to op amp offset has been greatly reduced compared to previous generations of multiplying DACs.

Tables 2 and 3 contain equations for evaluating the effects of op amp parameters on the LTC1599's accuracy when

configured in unipolar or bipolar modes of operation (Figures 1 and 3). These are the changes the op amp can cause to the INL, DNL, unipolar offset, unipolar gain error, bipolar zero and bipolar gain error. Table 4 contains a partial list of LTC precision op amps recommended for use with the LTC1599. The two sets of easy-to-use design equations simplify the selection of op amps to meet the system's specified error budget. Select the amplifier from Table 4 and insert the specified op amp parameters in either Table 2 or Table 3. Add up all the errors for each category to determine the effect the op amp has on the accuracy of the LTC1599. Arithmetic summation gives an (unlikely) worst-case effect. RMS summation produces a more realistic effect.

Op amp offset will contribute mostly to output offset and gain error and has minimal effect on INL and DNL. For the LTC1599, a  $500\mu V$  op amp offset will cause about 0.55LSB

INL degradation and 0.15LSB DNL degradation with a 10V full-scale range (20V range in bipolar). For the LTC1599 configured in the unipolar mode, the same  $500\mu V$  op amp offset will cause a 3.3LSB zero-scale error and a 3.45LSB gain error with a 10V full-scale range.

While not directly addressed by the simple equations in Tables 2 and 3, temperature effects can be handled just as easily for unipolar and bipolar applications. First, consult an op amp's data sheet to find the worst-case  $V_{OS}$  and  $I_{B}$  over temperature. Then, plug these numbers in the  $V_{OS}$  and  $I_{B}$  equations from Table 2 or Table 3 and calculate the temperature induced effects.

For applications where fast settling time is important, Application Note 74, entitled "Component and Measurement Advances Ensure 16-Bit DAC Settling Time," offers a thorough discussion of 16-bit DAC settling time and op amp selection.

Table 2. Easy-to-Use Equations Determine Op Amp Effects on DAC Accuracy in Unipolar Applications

| OP AMP                 | INL (LSB)                                          | DNL (LSB)                                          | UNIPOLAR OFFSET (LSB)                            | UNIPOLAR GAIN ERROR (LSB)                       |

|------------------------|----------------------------------------------------|----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|

| V <sub>OS</sub> (mV)   | V <sub>OS</sub> • 1.2 • (10V/V <sub>REF</sub> )    | V <sub>OS</sub> • 0.3 • (10V/V <sub>REF</sub> )    | V <sub>OS</sub> • 6.6 • (10V/V <sub>REF</sub> )  | V <sub>OS</sub> • 6.9 • (10V/V <sub>REF</sub> ) |

| I <sub>B</sub> (nA)    | I <sub>B</sub> • 0.00055 • (10V/V <sub>REF</sub> ) | I <sub>B</sub> • 0.00015 • (10V/V <sub>REF</sub> ) | I <sub>B</sub> • 0.065 • (10V/V <sub>REF</sub> ) | 0                                               |

| A <sub>VOL</sub> (V/V) | 10k/A <sub>VOL</sub>                               | 3k/A <sub>VOL</sub>                                | 0                                                | 131k/A <sub>VOL</sub>                           |

Table 3. Easy-to-Use Equations Determine Op Amp Effects on DAC Accuracy in Bipolar Applications

| OP AMP                | INL (LSB)                                           | DNL (LSB)                                           | BIPOLAR ZERO ERROR (LSB)                          | BIPOLAR GAIN ERROR (LSB)                          |

|-----------------------|-----------------------------------------------------|-----------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| V <sub>OS1</sub> (mV) | V <sub>OS1</sub> • 1.2 • (10V/V <sub>REF</sub> )    | V <sub>OS1</sub> • 0.3 • (10V/V <sub>REF</sub> )    | V <sub>0S1</sub> • 9.9 • (10V/V <sub>REF</sub> )  | V <sub>0S1</sub> • 6.9 • (10V/V <sub>REF</sub> )  |

| I <sub>B1</sub> (nA)  | I <sub>B1</sub> • 0.00055 • (10V/V <sub>REF</sub> ) | I <sub>B1</sub> • 0.00015 • (10V/V <sub>REF</sub> ) | I <sub>B1</sub> • 0.065 • (10V/V <sub>REF</sub> ) | 0                                                 |

| A <sub>VOL1</sub>     | 10k/A <sub>VOL</sub>                                | 3k/A <sub>VOL1</sub>                                | 0                                                 | 196k/A <sub>VOL1</sub>                            |

| V <sub>OS2</sub> (mV) | 0                                                   | 0                                                   | V <sub>0S2</sub> • 6.7 • (10V/V <sub>REF</sub> )  | V <sub>OS2</sub> • 13.2 • (10V/V <sub>REF</sub> ) |

| I <sub>B2</sub> (nA)  | 0                                                   | 0                                                   | I <sub>B2</sub> • 0.065 • (10V/V <sub>REF</sub> ) | I <sub>B2</sub> • 0.13 • (10V/V <sub>REF</sub> )  |

| A <sub>VOL2</sub>     | 0                                                   | 0                                                   | 65k/A <sub>VOL2</sub>                             | 131k/A <sub>VOL2</sub>                            |

Table 4. Partial List of LTC Precision Amplifiers Recommended for Use with the LTC1599, with Relevant Specifications

|               |                                     | Amplifier Specifications |                         |                            |                            |                      |                                  |                                             |                            |  |  |

|---------------|-------------------------------------|--------------------------|-------------------------|----------------------------|----------------------------|----------------------|----------------------------------|---------------------------------------------|----------------------------|--|--|

| AMPLIFIER     | <b>V<sub>OS</sub></b><br>μ <b>V</b> | I <sub>B</sub>           | A <sub>OL</sub><br>V/mV | VOLTAGE<br>NOISE<br>nV/√Hz | CURRENT<br>NOISE<br>pA/√Hz | SLEW<br>RATE<br>V/µs | GAIN BANDWIDTH<br>Product<br>MHz | t <sub>SETTLING</sub><br>with LTC1599<br>μs | POWER<br>DISSIPATION<br>mW |  |  |

| LT1001        | 25                                  | 2                        | 800                     | 10                         | 0.12                       | 0.25                 | 0.8                              | 120                                         | 46                         |  |  |

| LT1097        | 50                                  | 0.35                     | 1000                    | 14                         | 0.008                      | 0.2                  | 0.7                              | 120                                         | 11                         |  |  |

| LT1112 (Dual) | 60                                  | 0.25                     | 1500                    | 14                         | 0.008                      | 0.16                 | 0.75                             | 115                                         | 10.5/Op Amp                |  |  |

| LT1124 (Dual) | 70                                  | 20                       | 4000                    | 2.7                        | 0.3                        | 4.5                  | 12.5                             | 19                                          | 69/0p Amp                  |  |  |

| LT1468        | 75                                  | 10                       | 5000                    | 5                          | 0.6                        | 22                   | 90                               | 2.5                                         | 117                        |  |  |

Figure 1. Unipolar Operation (2-Quadrant Multiplication)  $V_{OUT} = 0V$  to  $-V_{REF}$

Figure 2. Noninverting Unipolar Operation (2-Quadrant Multiplication)  $V_{OUT} = 0V$  to  $V_{REF}$

Figure 3. Bipolar Operation (4-Quadrant Multiplication)  $V_{OUT} = -V_{REF}$  to  $V_{REF}$

#### **Precision Voltage Reference Considerations**

Much in the same way selecting an operational amplifier for use with the LTC1599 is critical to the performance of the system, selecting a precision voltage reference also requires due diligence. As shown in the section describing the basic operation of the LTC1599, the output voltage of the DAC circuit is directly affected by the voltage reference; thus, any voltage reference error will appear as a DAC output voltage error.

There are three primary error sources to consider when selecting a precision voltage reference for 16-bit applications: output voltage initial tolerance, output voltage temperature coefficient and output voltage noise.

Initial reference output voltage tolerance, if uncorrected, generates a full-scale error term. Choosing a reference with low output voltage initial tolerance, like the LT1236 ( $\pm 0.05\%$ ), minimizes the gain error caused by the reference; however, a calibration sequence that corrects for system zero- and full-scale error is always recommended.

A reference's output voltage temperature coefficient affects not only the full-scale error, but can also affect the circuit's INL and DNL performance. If a reference is chosen with a loose output voltage temperature coefficient, then the DAC output voltage along its transfer characteristic will be very dependent on ambient conditions. Minimizing the error due to reference temperature coefficient can be achieved by choosing a precision reference with a low output voltage temperature coefficient and/or tightly controlling the ambient temperature of the circuit to minimize temperature gradients.

As precision DAC applications move to 16-bit and higher performance, reference output voltage noise may contribute a dominant share of the system's noise floor. This in turn can degrade system dynamic range and signal-to-noise ratio. Care should be exercised in selecting a voltage reference with as low an output noise voltage as practical for the system resolution desired. Precision voltage references, like the LT1236, produce low output noise in the 0.1Hz to 10Hz region, well below the 16-bit LSB level in 5V

or 10V full-scale systems. However, as the circuit bandwidths increase, filtering the output of the reference may be required to minimize output noise.

Table 5. Partial List of LTC Precision References Recommended for Use with the LTC1599, with Relevant Specifications

| REFERENCE                | INITIAL<br>Tolerance | TEMPERATURE<br>DRIFT | 0.1Hz to 10Hz<br>NOISE |

|--------------------------|----------------------|----------------------|------------------------|

| LT1019A-5,<br>LT1019A-10 | ±0.05%               | 5ppm                 | 12μV <sub>P-P</sub>    |

| LT1236A-5,<br>LT1236A-10 | ±0.05%               | 5ppm                 | 3μV <sub>P-P</sub>     |

| LT1460A-5,<br>LT1460A-10 | ±0.075%              | 10ppm                | 20μV <sub>P-P</sub>    |

#### Grounding

As with any high resolution converter, clean grounding is important. A low impedance analog ground plane and star grounding should be used.  $I_{OUT2F}$  and  $I_{OUT2S}$  must be tied to the star ground with as low a resistance as possible. When it is not possible to locate star ground close to  $I_{OUT2F}$  and  $I_{OUT2S}$ , separate traces should be used to route these pins to star ground. This minimizes the voltage drop from these pins to ground caused by the code dependent current flowing to ground. When the resistance of these circuit board traces becomes greater than  $1\Omega$ , the circuit in Figure 4 eliminates voltage drop errors caused by high

resistance traces. This preserves the excellent accuracy (1LSB INL and DNL) of the LTC1599.

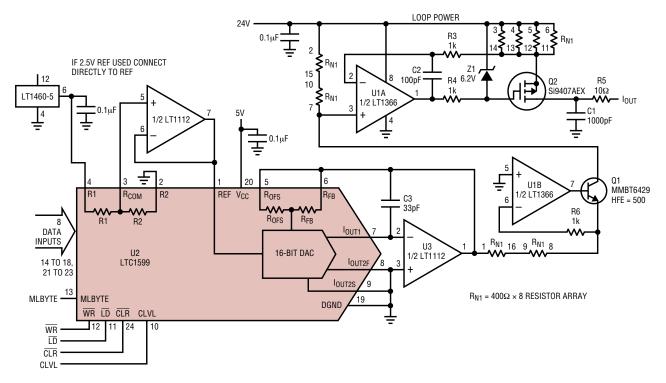

# A 16-Bit, 4mA to 20mA Current Loop Controller for Industrial Applications

Modern process control systems must often deal with legacy 4mA to 20mA analog current loops as a means of interfacing with actuators and valves located at a distance. The circuit in Figure 5 provides an output to a current loop controlled by an LTC1599, a 16-bit current output DAC. A dual rail-to-rail op amp (U1, LT1366) controls a P-channel power FET (Q2) to produce a current mirror with a precise 8:1 ratio as defined by a resistor array. The input current to this mirror circuit is produced by a grounded base cascode stage using a high gain transistor (Q1). The use of a bipolar transistor in this location results in an error term associated with U1B and Q1's base current (-0.2% for the device shown). For control applications however, absolute accuracy of the output to an actuator is usually not required. If a higher degree of absolute accuracy is required, Q1 can be replaced with an N-channel JFET; however, this requires a single amplifier at U1B with the ability to drive the gate below ground. An enhancement mode N-channel FET can be used in place of Q1 but MOSFET leakage current must be considered and gate overdrive must be avoided.

Figure 4. Driving I<sub>OUT2F</sub> and I<sub>OUT2S</sub> with a Force/Sense Amplifier

The output current of the DAC is converted to a voltage via U3 (LT1112), producing 0V to -2.5V at Pin 1 of U3. The resulting current in Q1 is determined by two elements of resistor array,  $R_{N1}$  (3mA max). The emitter of Q1 is maintained at 0V by the action of U1B.

In applications that do not require 16-bit resolution and accuracy, the LTC1599 can be replaced by the 14-bit parallel LTC1591. Furthermore, the resistor array can be substituted with discrete resistors, and Q2 could be replaced by a high gain bipolar PNP; for example, an FZT600 from Zetex.

No trim is provided a shown, as it is expected that software control is preferable. The output range of 4mA to 20mA is defined by software, as the full output range is nominally 0mA to 24mA.

U1 is a rail-to-rail amplifier that can operate on suppy voltages up to 36V. This defines the maximum voltage on the loop power. If higher loop voltages are required, a separate low power amplifier at U1A, powered by a zener regulated supply and referenced to loop power, would allow voltages up to the breakdown voltages of Q1 and Q2.

In the example shown, the use of a dual op amp requires a zener clamp to protect the gate of the MOS power transistor. If a separate shunt-regulated supply is provided for the amplifier replacing U1A, the gate clamp (Z1) is not required.

As shown, this topology uses the LTC1599's internal divider (R1 and R2) to reduce the reference from 5V to 2.5V. If a 2.5V reference is used, it can be connected directly to REF (Pin 1). Alternatively, if the op amp is powered such that it has -10V output capability, the divider and amplifier prior to the REF input are not required and  $R_{OFS}$  can be used for other purposes such as offset trim. The two  $R_{\text{N1}}$  resistors at the emitter of Q1 must be changed in this case.

Note that the output of the current transmitter shows a network that is intended to provide a first line of defense against ESD and prevent oscillation (1000pF and  $10\Omega$ ) that could otherwise occur in the power MOSFET if lead inductance were more than a few inches. C1 should be as close as possible to Q2. Using MOSFETs that have higher threshold voltages may require changing Z1 in order to allow full current output.

Figure 5. 16-Bit Current Loop Controller for Industrial Applications

#### A 16-Bit General Purpose Analog Output Circuit

Industrial applications often use analog signals of OV to 5V, 0V to 10V,  $\pm$ 5V or  $\pm$ 10V. The topology in Figure 6 uses an LTC1599 to produce a universal analog output, capable of operation over all these ranges, with only software configuration. High precision analog switches are used to provide uncompromising stability in all ranges and matched resistors internal to the LTC1599 are used, as well as a configuration that minimizes the effects of channel resistance in the switches. Note that in all cases the analog switches have minimal current flowing through them. The use of unbuffered analog switches in series with the feedback/divider resistors would result in an error because of temperature coefficient mismatch between the internal DAC resistors and the switch channel resistances. as well as the channel resistance variation over the signal range. Quad analog switch U3 (DG212B) allows configuration of feedback terms and selection of the reference voltage. Switch C allows the buffered reference voltage to be injected into the summing node via Pin 5 (R<sub>OFS</sub>) for bipolar outputs. When active, switch D places R<sub>OFS</sub> in parallel with R<sub>FB</sub>, producing an output at full scale voltage equal to the voltage at the REF pin of the LTC1599.

The other switches in U3 (A and B) are used to select the 10V reference produced by the LT1019, or 5V produced by the R3 and R4 divider.

An inexpensive precision divider can be implemented using an 8-element resistor array, paralleling four resistors for R3 and four resistors for R4. Symmetry in the interconnection of these resistors will ensure compensation for temperature gradient across the resistor array. An

alternative to a resistor divider is the LTC1043 switched capacitor building block. It can be configured as a high precision divide-by-2. Please consult the LTC1043 data sheet for more information.

The NOR gate (U4) ensures that switches C and D are not enabled simultaneously. This eliminates contention between the reference buffer and the output amplifier.

This topology can be modified to accept a high current buffer following the LT1112, if higher output current levels are required or difficult loads need be driven. Adjustment of  $C_{FB}$ 's value may be required for the buffer amplifier chosen.

Note that the analog switches must handle the full output swing in this configuration, but there is a variety of suitable switches on the market including the LTC201. The DG212B as shown is a newer generation part with lower leakage, providing a performance advantage.

The DG333A, a quad single-pole, double-throw switch, could be used for a 2-channel version similar to this circuit. Alternatively, a single channel can be created with the additional switches used as switched capacitor divide-by-2, as shown on the LTC1043 data sheet. In choosing analog switches, keep in mind the logic levels and the signal levels required.

Table 1. Configuration Settings for the Various Output Ranges

| V <sub>OUT</sub> MODE | REFSEL | BIPOLAR/UNIPOLAR | GAIN |

|-----------------------|--------|------------------|------|

| 0V to 5V              | 1      | 0                | 0    |

| 0V to 10V             | 1      | 0                | 1    |

| -5V to 5V             | 1      | 1                | 1    |

| -10V to 10V           | 0      | 1                | 1    |

# LTC1599

**APPLICATIONS INFORMATION**

#### BIPOLAR/UNIPOLAR 15V U1D 1/4 LT1114 U1C 1/4 LT1114 U3D ₹R3 100k ÷ U5 LT1019-10 U1B 1/4 LT1114 REF V<sub>CC</sub> R<sub>COM</sub> Rofs R<sub>OFS</sub> R<sub>FB</sub> $R_{FB}$ 8 DATA INPUTS I<sub>OUT1</sub> R1 = R2 = 5k U3A TO U3D = 1/4 DG212B U4A, U4B = 1/4 HC02 LT1019 PINOUT FOR SO-8 PACKAGE LT1114 PINOUT FOR SO PACKAGE U1A 1/4 LT1114 U2 LTC1599 16-BIT DAC $V_{OUT}$ 14 TO 18, 21 TO 23 I<sub>OUT2F</sub> OPTIONAL HIGH CURRENT BUFFER LT1010 LT1206 LT1210 MLBYTE 13 MLBYTE WR LD CLR CLVL -15V 1599 F06 12 11 24 WR $\overline{\mathsf{LD}}$ CLVL

Figure 6. 16-Bit General Purpose Analog Output Circuit

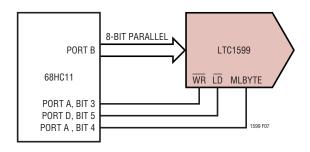

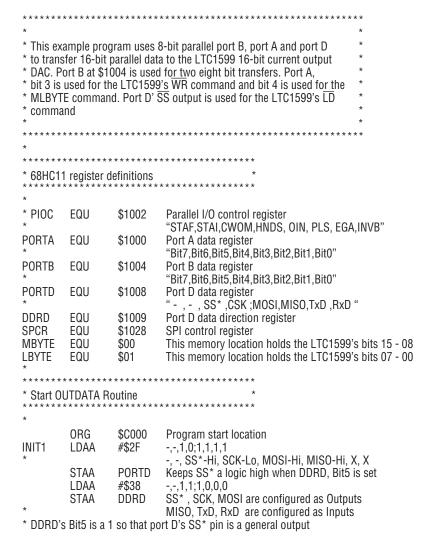

#### Interfacing to the 68HC11

The circuit in Figure 7 is an example of using the 68HC11 to control the LTC1599. Data is sent to the DAC using two 8-bit parallel transfers from the controller's Port B. The WR signal is generated by manipulating the logic output on Port A's bit 3, the MLBYTE command is sent to the DAC using Port A's bit 4, and the LD command comes from the SS output on Port D's bit 5.

The sample listing 68HC11 assembly code in Listing A is designed to emulate the Timing Diagram found earlier in this data sheet. After variable declaration, the main portion of the program retrieves the <u>least</u> significant byte from memory, forces MLBYTE and WR to a logic low, <u>and</u> then writes the low byte data to Port B. It then sets WR and

Figure 7. Using the 68HC11 to Control the LTC1599

MLBYTE high. Next, the most significant byte is copied from memory and  $\overline{WR}$  is again asserted low. The high byte is written to Port B and  $\overline{WR}$  is returned high. The transfer of the 16 bits is completed by cycling the  $\overline{LD}$  input low and then high using the  $\overline{SS}$  output on Port D.

| GETDATA | PSHY<br>PSHA                | <b>#</b> \$1,000            | Catura in day                                                        |                                                                                                                                        |

|---------|-----------------------------|-----------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| *       | LDY                         | #\$1000                     | Setup index                                                          |                                                                                                                                        |

| *****   | ******                      | *****                       | ******                                                               |                                                                                                                                        |

|         | e DAC data<br>to the LTC    | 1 from mem<br>1599<br>***** | ory and<br>********                                                  |                                                                                                                                        |

| *       | LDAA<br>BCLR                | LBYTE<br>PORTA,Y            | %00010000                                                            | Retrieve the least significant byte from memory<br>This sets PORTA, Bit4 output to a logic<br>low, forcing MLBYTE input to a logic low |

|         | BCLR<br>STAA<br>BSET        | PORTB                       | %00001000<br>%00001000                                               | This forces a low on the LTC1599's WR pin Transfer the least significant byte to the DAC This forces a high on the LTC1599's WR pin    |

| *       | BSET                        |                             | %00010000                                                            | This sets PORTA, Bit4 output to a logic high, forcing MLBYTE to a logic high Retrieve the most significant byte from memory            |

|         | BCLR<br>STAA<br>BSET        | PORTA,Y<br>PORTB            | %00001000<br>%00001000                                               | This forces a low on the LTC1599's WR pin Transfer the most significant byte to the DAC This forces a high on the LTC1599's WR pin     |

| *       |                             | •                           |                                                                      |                                                                                                                                        |

| *****   |                             | uctions exe                 | ***************                                                      | **                                                                                                                                     |

|         |                             | ning the dat                |                                                                      |                                                                                                                                        |

|         | s just load                 |                             | *****                                                                | *                                                                                                                                      |

| *       |                             |                             |                                                                      |                                                                                                                                        |

|         | BCLR                        |                             | %00100000                                                            | LD goes low                                                                                                                            |

| *       | BSET                        | PORTD,Y                     | %00100000                                                            | and returns high                                                                                                                       |

|         | _                           |                             | ******                                                               | **                                                                                                                                     |

|         |                             | ine complet                 |                                                                      | *                                                                                                                                      |

| *       | DIII A                      |                             |                                                                      |                                                                                                                                        |

|         | PULA<br>PULY<br>PULX<br>RTS |                             | Restore the A regist<br>Restore the Y regist<br>Restore the X regist | er                                                                                                                                     |

## TYPICAL APPLICATION

16-Bit V<sub>OUT</sub> DAC Programmable Unipolar/Bipolar Configuration

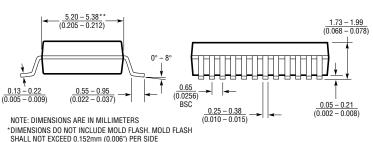

# PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

#### G Package 24-Lead Plastic SSOP (0.209) (LTC DWG # 05-08-1640)

sn1599 1599fs

\*\*DIMENSIONS DO NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.254mm (0.010") PER SIDE

#### TYPICAL APPLICATION

17-Bit Sign Magnitude DAC with Bipolar Zero Error of 140µV (0.92LSB at 17 Bits) at 25°C

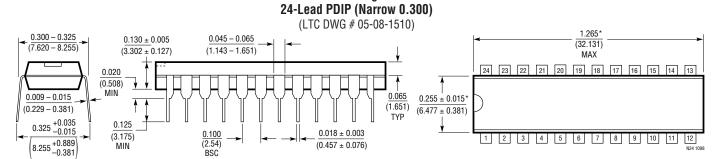

### PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

N Package

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

#### RELATED PARTS

| PART NUMBER     | DESCRIPTION                            | COMMENTS                                                                               |

|-----------------|----------------------------------------|----------------------------------------------------------------------------------------|

| LT1236          | Precision Reference                    | 0.05% Initial Accuracy, 5ppm Temperature Drift                                         |

| LT1468          | 16-Bit Accurate Op Amp                 | 90MHz Gain Bandwidth, 22V/µs Slew Rate                                                 |

| LTC1591/LTC1597 | Parallel 14/16-Bit Current Output DACs | On-Chip 4-Quadrant Resistors                                                           |

| LTC1595/LTC1596 | Serial 16-Bit Current Output DACs      | Low Glitch, ±1LSB Maximum INL, DNL                                                     |

| LTC1650         | 16-Bit Voltage Output DAC              | Low Power, Deglitched, 4-Quadrant Multiplying V <sub>OUT</sub> DAC, ±4.5V Output Swing |

| LTC1657         | 16-Bit Parallel Voltage Output DAC     | Low Power, 16-Bit Monotonic Over Temperature, Multiplying Capability                   |

| LTC1658         | 14-Bit Rail-to-Rail Micropower DAC     | Low Power Multiplying V <sub>OUT</sub> DAC in MSOP. Output Swings from GND to REF.     |